- 您现在的位置:买卖IC网 > Sheet目录1905 > ATMEGA8HVA-4CKU (Atmel)MCU AVR 8K FLASH 4MHZ 36-LGA

108

8024A–AVR–04/08

ATmega8HVA/16HVA

Bit 5 - CADUB: CC-ADC Update Busy

The CC-ADC operates in a different clock domain than the CPU. Whenever a new value is writ-

ten to CADCSRA or CADRC this value must be synchronized to the CCADC clock domain.

Subsequent writes to these registers will be blocked during this synchronization. Synchroniza-

tion of one of the registers will block updating of all the others. The CADUB bit will be read as

one while any of these registers is being synchronized, and will be read as zero when neither

register is being synchronized.

Bits 4:3: CADAS[1:0]: CC-ADC Accumulate Current Select

The CADAS bits select the conversion time for the Accumulate Current output as shown in Table

19-1.

Note:

1. The actual value depends on the actual frequency of the Slow RC oscillator, see

.

Bits 2:1: CADSI[1:0]: CC-ADC Current Sampling Interval

The CADSI bits determine the current sampling interval for the Regular Current detection as

shown in Table 19-2.

Notes:

1. The actual value depends on the actual frequency of the Slow RC oscillator, see ”Slow RC

2. Sampling time ~ 12 ms.

Bit 0 - CADSE: CC-ADC Sampling Enable

When the CADSE bit is written to one, the ongoing CC-ADC conversion is aborted, and the

CCADC enters Regular Current detection mode.

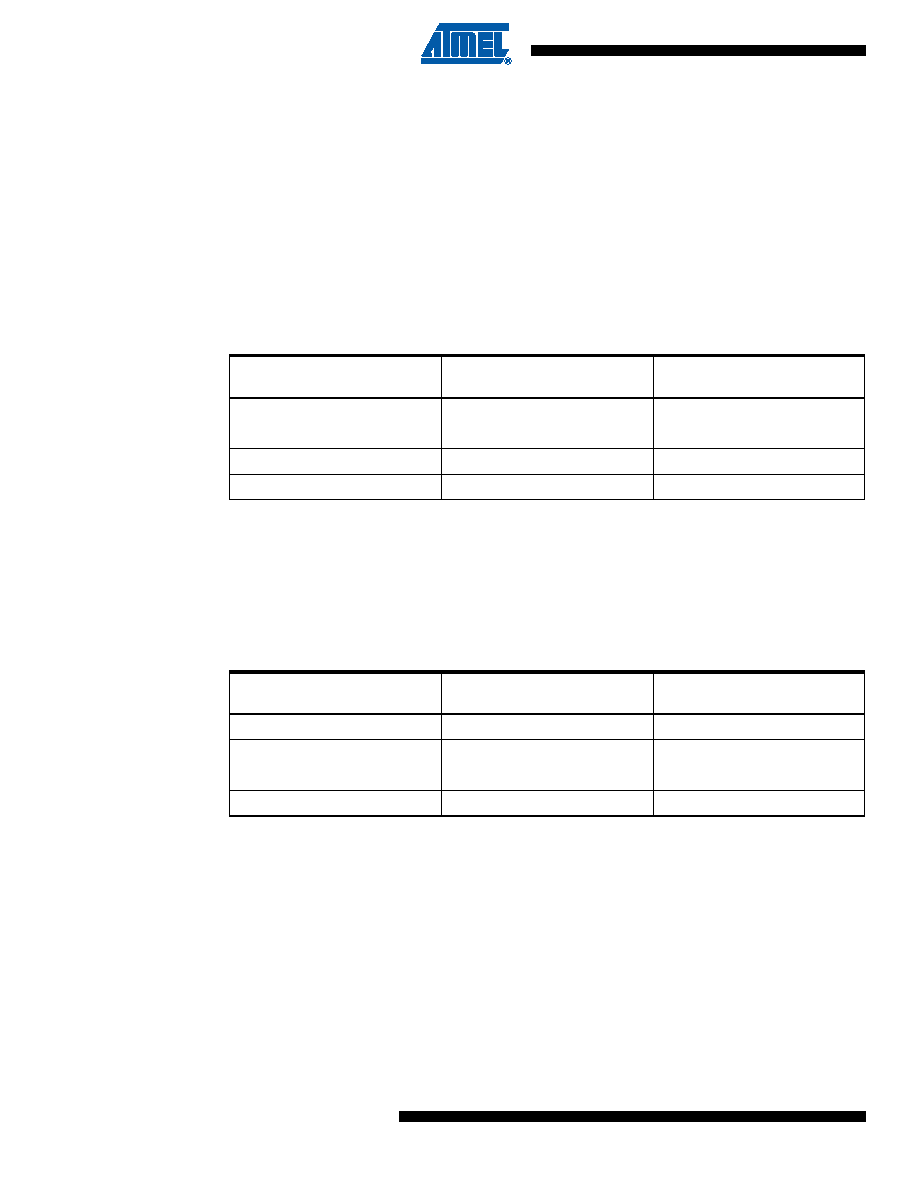

Table 19-1.

CC-ADC Accumulate Current Conversion Time

CADAS[1:0]

CC-ADC Accumulate Current

Conversion Time(1)

Number of CC-ADC Clock

Cycles

00

125 ms

4096

01

250 ms

8192

10

500 ms

16384

11

1s

32768

Table 19-2.

CC-ADC Regular Current Sampling Interval

CADSI[1:0]

CC-ADC Regular Current

Sampling Interval(1)(2)

Number of CC-ADC Clock

Cycles

00

250 ms (+ sampling time)

8192 (+ sampling time)

01

500 ms (+ sampling time)

16384 (+ sampling time)

10

1s (+ sampling time)

32768 (+ sampling time)

11

2s (+ sampling time)

65536 (+ sampling time)

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

ATSAM3N4AA-AU

MCU FLASH 48-QFP

ATSAM3SD8CA-CU

IC MCU 2X256KB CORTEX-M3 100-QFN

ATSAM3U1EB-CU

IC MCU 64KB CORTEX-M3 144-TFBGA

ATSAM3X8EA-CU

IC MCU 2X256KB CORTEX-M3 144-BGA

ATTINY12V-1SUR

IC AVR MCU 1K FLASH 4MHZ 8-SOIC

ATTINY13-20SQR

IC MCU AVR 1KB FLASH 20MHZ 8SOIC

ATTINY13A-MMUR

MCU AVR 1KB FLASH 20MHZ 10DFN

ATTINY13V-10SUR

MCU AVR 1KB FLASH 10MHZ 8SOIC

相关代理商/技术参数

ATMEGA8HVA-4CKUR

功能描述:8位微控制器 -MCU AVR 8KB FLSH 512B EE 1KB SRAM - 4 MHZ RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA8HVA-4TU

功能描述:8位微控制器 -MCU AVR 8KB, 512B EE 4MHz 1KB SRAM 1.8-9V RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA8HVA-4TUR

功能描述:8位微控制器 -MCU AVR 8KB FLSH 512B EE 1KB SRAM - 4 MHZ RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA8HVD-4MX

功能描述:8位微控制器 -MCU AVR 8KB, 512B EE 4MHz 1KB SRAM 2.1-8V

RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA8L-8AC

功能描述:8位微控制器 -MCU AVR 8K FLASH 512B EE 1K SRAM ADC 3V RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA8L8AI

制造商:Atmel Corporation 功能描述:

ATMEGA8L-8AI

功能描述:8位微控制器 -MCU AVR 8K FLASH 512B EE 1K SRAM ADC 3V RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA8L-8AJ

功能描述:IC MCU AVR 8K 5V 8MHZ 32-TQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - 微控制器, 系列:AVR® ATmega 标准包装:9 系列:87C 核心处理器:8051 芯体尺寸:8-位 速度:40/20MHz 连通性:UART/USART 外围设备:POR,WDT 输入/输出数:32 程序存储器容量:32KB(32K x 8) 程序存储器类型:OTP EEPROM 大小:- RAM 容量:256 x 8 电压 - 电源 (Vcc/Vdd):4.5 V ~ 5.5 V 数据转换器:- 振荡器型:内部 工作温度:0°C ~ 70°C 封装/外壳:40-DIP(0.600",15.24mm) 包装:管件